|

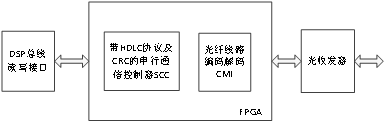

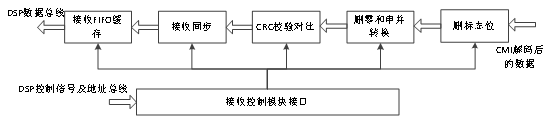

摘要:设计了一种基于FPGA的光纤数字接口系统,介绍了运用FPGA实现的HDLC发送功能模块和接收功能模块以及CMI编码解码模块,该系统可以有效利用FPGA片内硬件资源,无需外围电路,高度集成且操作简单。 关键词:电流纵差保护;FPGA;HDLC;CMI 0. 引言 电流纵差保护广泛应用于微机继电保护中,由于需要在输电线两端之间传输三相电流及时间等数据,其关键就是保证传输数据的准确性和实时性,不受外界电磁、气候等影响。随着电压等级的提高,白色噪声、脉冲干扰、电磁场干扰越来越大,极易影响两端的通讯质量。光纤通讯具有频带宽、容量大、传输损耗小、中继距离长、抗强电磁干扰等优点,因此光纤通讯为两端数据的可靠传输提供了保证。 1. 系统设计 光纤纵差保护装置的光纤数字接口是装置中重要组成部分,在进行光纤数字接口设计时,我们没有采用传统的芯片堆砌设计方法,而且运用大规模可编程门阵列(FPGA)来实现。在FPGA内部,主要有具有HDLC协议及CRC-16的串行通信控制器(SCC),和光纤线路的编码解码(CMI)。光收发器采用RTXM154TL芯片,硬件电路框图如图1所示。

图1 用FPGA实现的光纤数字接口硬件电流框图 接收过程:光收发器的接收端通过光纤把接收过来的光信号转换为电信号,此时接收的电信号已经编过码,经过CMI解码后送至SCC内部接收FIFO,实现HDLC解码和串并转换后,由DSP直接读走数据。 发送过程:DSP通过数据总线把需要发送的数据写入SCC的发送FIFO中,SCC根据设定好的HDLC协议,把并行数据转换为串行帧,发送到CMI,经CMI编码后送至光收发器,电信号转换为光信号经过光纤传至对侧。 2. SCC的设计 HDLC协议是高级数据链路层协议,是构成SCC的主要部分,在HDLC通信方式中,所有信息都是以帧的形式传送的,HDLC帧格式如表1所列。 表1 HDLC帧格式示意图 标志字 | 地址段 | 控制段 | 信息段 | CRC校验 | 标志字 | 01111110 | 8bit | 8bit | 可变长度 | 16bit | 01111110 |

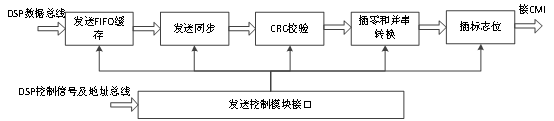

(1)标志字 HDLC协议规定,所有信息传输必须以一个标志字开始,且以同一个标志字结束,这个标志字是01111110(0x7E)。开始标志到结束标志之间构成一个完整的信息单位,称为一帧。接收方可以通过搜索01111110来探知帧的开始和结束,以此建立帧同步。在帧与帧之间的空载期,可连续发送标志字来做填充。 (2)信息段及“0”比特插入技术 HDLC帧的信息长度是可变的,可传送标志字以外的任意二进制信息。为了确保标志字是独一无二的,发送方在发送信息时采用“0”比特插入技术,即发送方在发送除标志字符外的所有信息时(包括校验位),只要遇到连续的5个“1”就自动插入一个“0”;反之,接收方在接收数据时,只要遇到连续的5个“1”,就自动将其后的“0”删掉。“0”比特插入和删除技术也使得HDLC具有良好的传输透明性,任何比特代码都可传输。 (3)地址段及控制段 地址字段用于标识接收该帧的地址;控制字段用来表示命令和响应的类别和功能。 (4)CRC校验 HDLC采用CCITT 标准的16位循环冗余校验码(CRC-16)进行差错控制,其生成多项式为

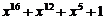

HDLC差错校验指对整个帧的内容作CRC循环冗余校验, 即对在纠错范围内的错码进行纠正, 对在校错范围内的错码进行校验,但不能纠正。标志位和按透明规则插入的所有“0” 不在校验的范围内。 2.1 HDLC发送模块 发送模块主要分为发送控制接口模块、发送FIFO缓存模块、发送同步模块、CRC校验生成模块、插零和并串转换模块、插标志位模块。发送模块示意图如图2所示。

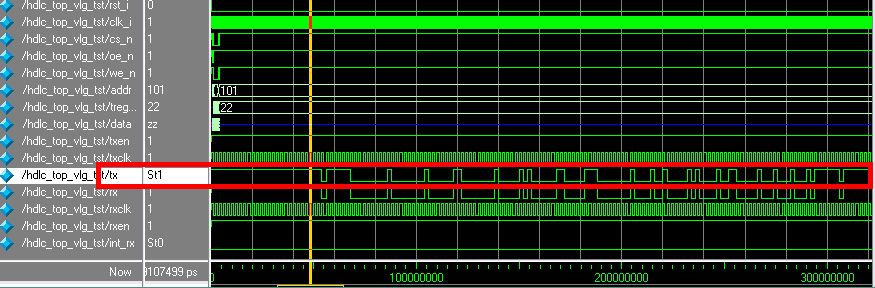

图2 发送功能模块示意图 (1)发送FIFO缓存模块可以存入DSP发送的数据,根据光纤差动要传输的数据,缓存大小为256bytes足够。本设计中,串行发送的速率为了适用于复接设备E1接口,把串行的速率设为2Mbit/s。而DSP读写总线数据的速率远大于2Mbit/s,因此主时钟和串行收发时钟的频率相差较大,而使用FIFO可以有效的协调两者的频率差带来的同步问题。 (2)发送同步模块负责控制系统时钟和串行发送时钟的同步,使相关控制信号完成高低速的匹配。每个进程都是串行时钟或者系统时钟的上升沿到来时进行高速和低速或者低速和高速的转换。 (3)CRC校验模块负责生成CCITT标准的CRC-16码,附加到数据后面。 (4)插零模块是为了区分帧头和帧尾的标志位,保证数据链路的透明传输(即可以传输任意组合的比特率),在发送端对传输数据进行”0”比特填充。因为帧头和帧尾为“01111110”,因此当帧连续传输了5个“1”比特后,插入一个“0”比特,可避免与标志位相同。 插零和并串转换的进程:异步置位,时钟上升沿到来时利用移位寄存器,进行8比特数据的并串转换,对连续的5比特数据求与运算,5个“1”比特之后,插入一个“0”比特,此时以为寄存器暂停移位。 (5)插标志位主要是对待发送的数据进行帧头尾的添加。 图3为发送模块的时序仿真图。发送的数据为0~10。

图3 发送模块时序仿真图 2.2 HDLC接收模块 接收模块主要分为接收控制接口模块、接收FIFO缓存模块、接收同步模块、CRC校验对比模块、删零和串并转换模块、删标志位模块。接收模块示意图如图4所示。

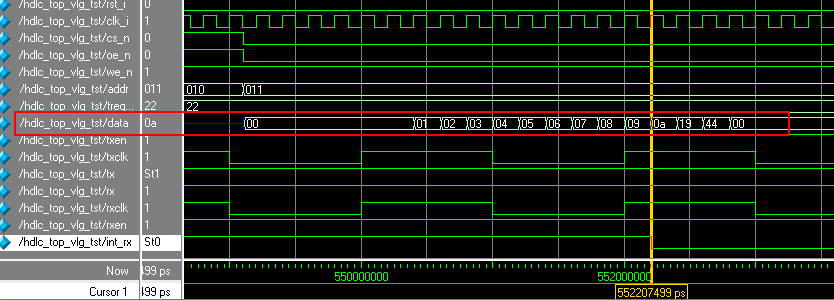

图4 接收功能模块示意图 (1)删标志位模块负责检测发送的帧头,确定起始边界,把CMI解码后的输入数据的帧头和帧尾删去。 (2)删零和串并转换模块中对比特流中的连续“1”比特进行计数,然后用于删零判断、检测帧结束标志和检测帧中断标志的功能。计数器和下一比特在不同值组合下所对应的含义如下: 1 当计数器的值为6,且下一接收比特为“0”,表明检测到帧结束标志。 2 当计数其的值为5,且下一接收比特为“0”,表明比特“0”应该删去。 3 当计数器的值为6,且下一接收比特为“1”,表明检测到中断标志。 (3)CRC校验对比模块把接收到的数据再进行CRC-16计算,其结果与接收到的CRC-16相比较,如果相同,则表示传输数据正确,否则舍弃该帧。 (4)接收同步模块和发送同步模块一样,模块负责控制系统时钟和串行接收时钟的同步,使高低速速度转换。 (5)接收FIFO缓存模块是把接收的数据存入FIFO缓存,并通知DSP可读取数据,DSP发生外部中断后把数据读走。 图5为接收模块的时序仿真图。接收的数据为0~10。

图5 接收模块时序仿真图 3. CMI编码和解码设计 光纤线路中线路码型传输性能的好坏直接影响光系统的传输性能。传输性能好的线路码型应该符合比特序列独立性好、功率谱密度中的高低频成分少、定时成分多、直流电平比较恒定、误码扩展系数小、码结构均匀等特征。适于光线路传输的码型比较多,本设计采用CMI码型。其变换模式为:“0”码变换为“01”,“1”码变换为交替的“00”和“11”码。 4. 结束语 与传统的芯片电路相比,采用大规模可编程门阵列(FPGA)芯片具有以下一些优点: (1)通信板结构简单,便于硬件设计,只需一块FPGA芯片可完成以上设计,占用PCB板空间小。 (2)可实现各功能模块之间的无缝连接。由于各功能模块的逻辑均在一个芯片内部完成,不存在相互之间电平匹配问题。 (3)时序控制简单。在芯片内部只需进行同意的时序控制即可,不需要考虑对不同的芯片进行不同的时序控制。 (4)可靠性高。采用FPGA芯片消除了由于不同芯片厂家生产的芯片的参数不同而造成通信不稳定现象,提高了通信的稳定性能。 本文采用了FPGA实现的SCC和CMI功能,调试结果表明,该系统操作简单、使用灵活、能够很好地应用于电力系统继电保护光纤通讯系统中。

|